Vendor Portfolio

Xilinx, now part of AMD, is a provider of FPGA (Field Programable Gate Arrays) devices. They provide a comprehensive suite of development tools for FPGA design and development. They have a plethora of multi-node FPGAs with special graded options for automotive, defence and space applications. Xilinx’s current multi-node portfolio

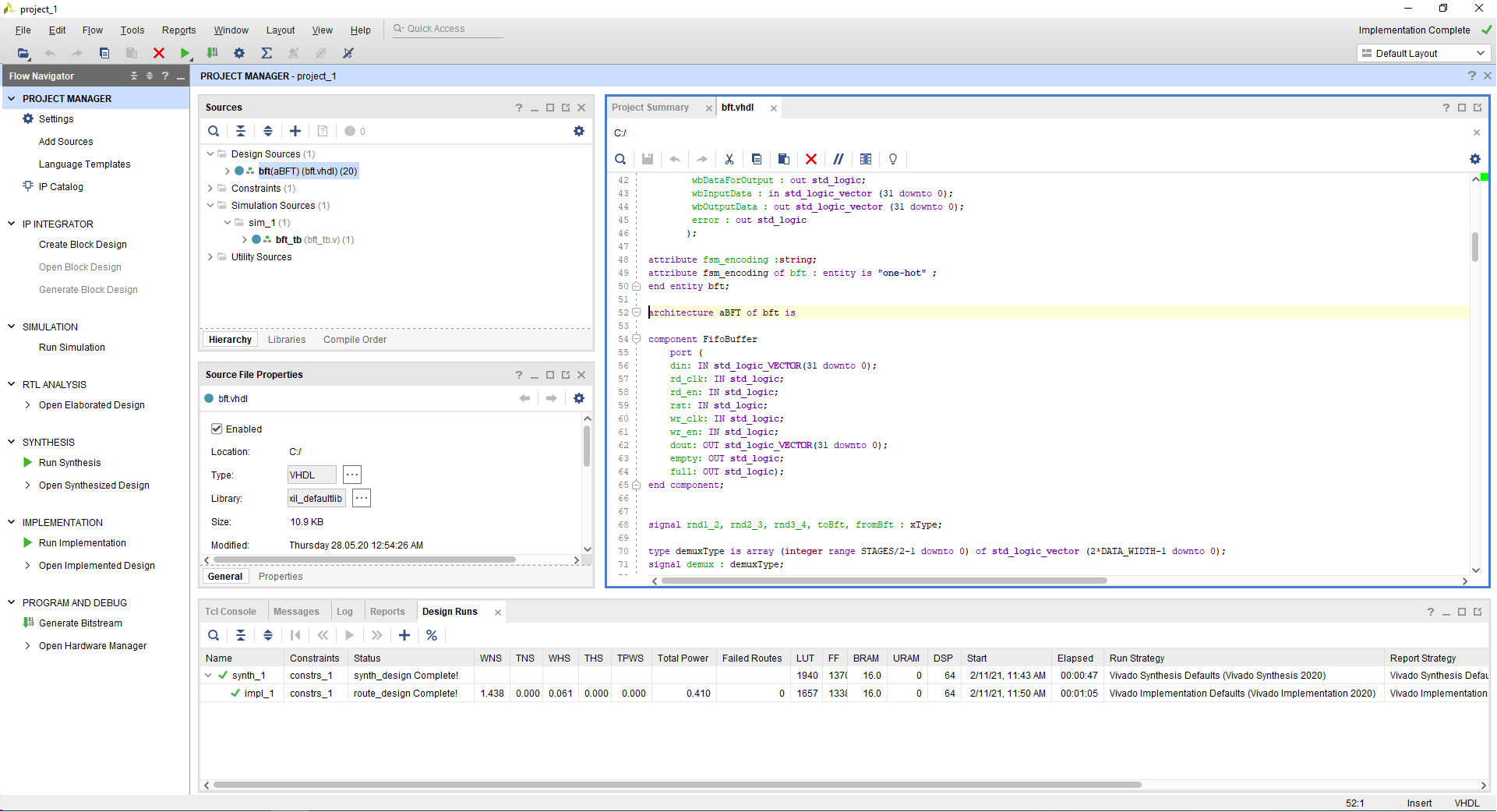

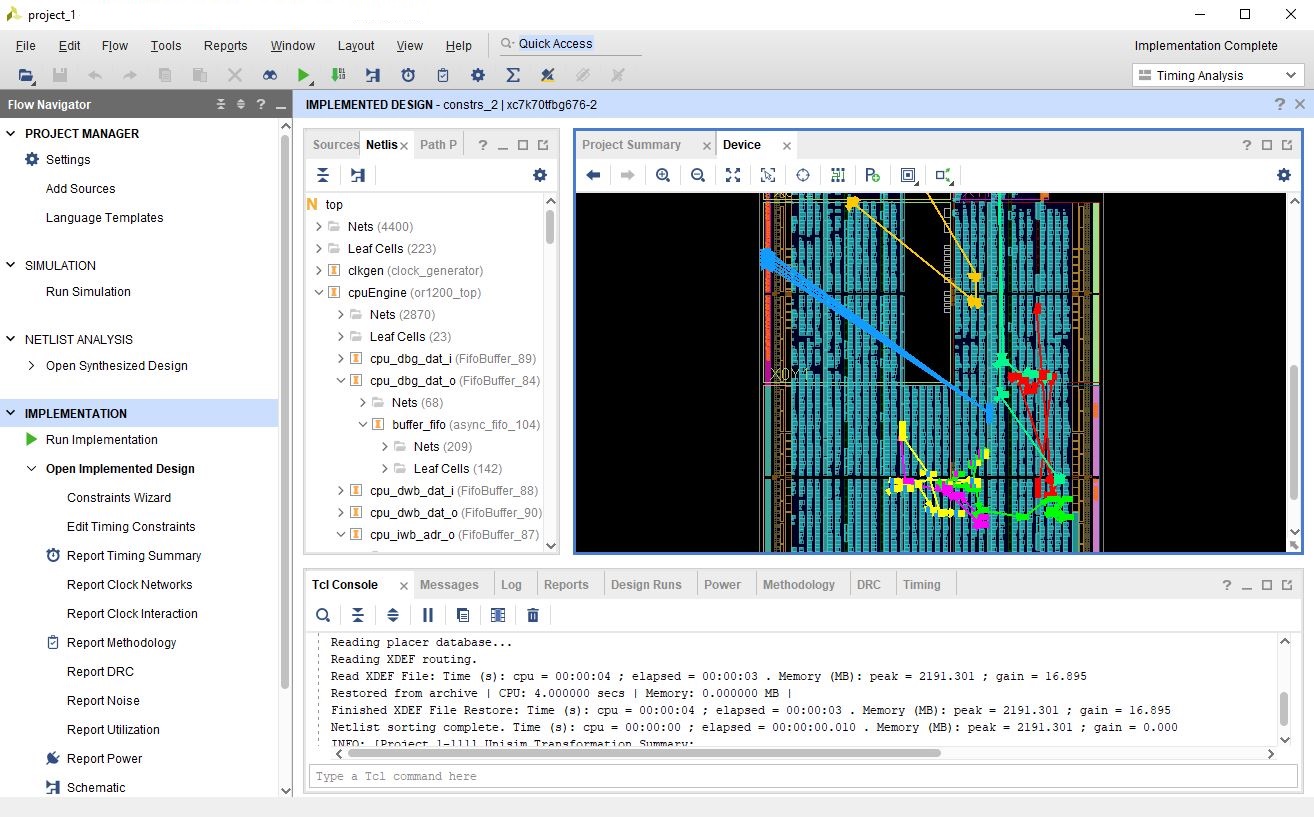

Vivado ML with Model Composer

Vivado ML is an HDL to FPGA implementation tool that has replaced Vivado HLx edition since version 2021.1. Vivado ML has the same functionality as Vivado HLx enterprise edition (see below) with improved performance via machine learning algorithms. Vivado ML includes Model Composer and Vitis HLS as standard.

Vivado ML provides support for all HLx devices along with:

- Versal AI Core Series: - XCVC1902 and XCVC1802

- Versal Prime Series: - XCVM1802

- Virtex UltraScale+ HBM device: XCVU57P

Vivado ML with Model Composer supported operating systems (x86 and x86-64bit):

- Windows 7 SP1 Professional (64-bit), English/Japanese

- Windows 10.0 Fall Creators update (version 1709), 10.0 Version 1803 (64-bit), English/Japanese.

- Red Hat Enterprise Workstation/Server 7.2, 7.3, and 7.4 (64-bit)

- SUSE Linux Enterprise 11.4 and 12.3 (64-bit)

- CentOS 7.2, 7.3, and 7.4 (64-bit)

- Ubuntu Linux 16.04.3 LTS (64-bit)

Vivado Design Suite HLx Edition

Vivado HLx Edition (succeeded by ML edition) integrates Vivado HLS as part of the suite allowing for C/C++ languages to be utilised for both HDL design and verification. Vivado supports the 7 Series and zynq Xilinx devices (Artix, Kintex, Virtex, Spartan) with options for Ultrascale, low voltage and MPSoCs also available.

Last version of Vivado HLx (2020.3) comes with versal platforms, Pentalinux, Block Design container, Dynamic Function eXchange, Vitis HLS (with an add-on for MATLAB and Simulink).

Vivado Design Suite HLx Edition supported operating systems (x86 and x86-64bit):

- Windows 10.0: Update 1809, 1903 and 1909

- Red Hat enterprise workstation/server: Versions 7.4 to 7.7 and 8.1 64-bit

- CentOS: Versions 7.4 to 7.7 and 8.1 64bit

- SUSE Linux enterprise 12.4 64-bit

- Amazon Linux 2, AL2, LTS 64-bit

- Ubuntu Linux 6.04.5, 16.04.6, 18.04.1, 18.04.2, 18.04.3, and 18.04.4 LTS 64-bit

The current and previous Vivado documentation can be found here

Vivado HLS – Integrated into Vivado ML and HLx Editions

Xilinx’s high level synthesis tool allows for software to Hardware conversion, testing and implementation. Vivado HLS has been developed for use with C, C++ and SystemC, allowing for these languages to be utilised for both HDL design and verification.

Please be aware, SystemC is no longer supported past version 2019.x.

Other Xilinx products available:

- Xilinx SDK – Software development kit and Integrated Development Environment (IDE) for embedded software applications (targeting Xilinx’s embedded processors). Works with hardware designs created in the Vivado design suite.

- System Generator for DSP – allows the designing, testing and implementation of high-performance DSP algorithms.

- Xilinx ISE – Discontinued, last update October 2013, is the previous software for Synthesis of HDL designs. Has since been replaced by Vivado and Vitis.

Xilinx licenses are generated by the EUROPRACTICE site representative, or authorized user, through the Xilinx website. The site representative/authorized user can generate floating or node-locked license files as required from the pool of unallocated seats. It is not necessary to specify the type of license (floating/node locked) required when placing an order, only the number of seats required.

Please go to Generate Xilinx Licenses to manage your licenses.