Genio - Chiplet and Packaging Co-Design Tools

The MZ Technologies Genio product family is aimed at reducing the time to design for complex Chiplet and 3DIC heterogeneous IC systems, through an improved level of management, automation and optimisation. Genio includes features to help accomplish the required area, power and performance requirements of the chiplet, through multi level co-design of die, interconnect interposer, and surrounding PCB area. Components are integrated through standard formats including LEF, GDS, DEF, AIf, Verilog, and TXT/CSV file, and are compatible with major EDA design platforms.

Feature Highlights

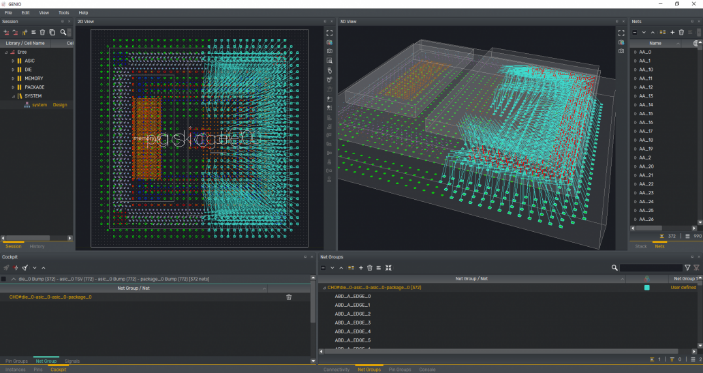

- Integrated environment for Chiplet and package implementation and analysis.

- Interconnect manager which represents and maintains the interconnect model of the package

- Cross-Hierarchical 3D-aware pathfinding engine which identifies the best interconnect connections, optimising the connections in the package.

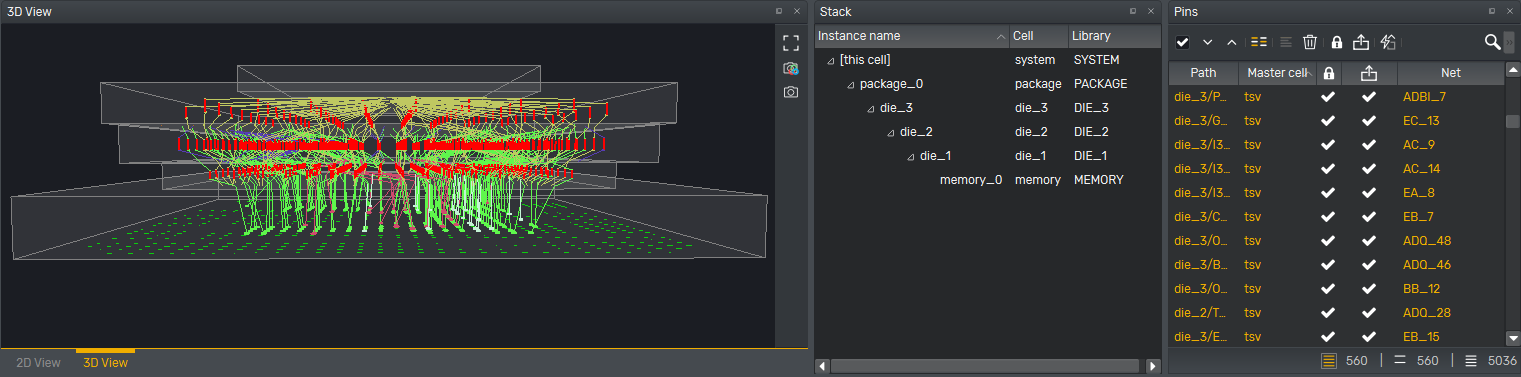

- 3D visualisation of complete system.

- What if exploration and analysis.

- System Wide I/O planning and optimisation.

- ASIC pad ring layout optimisation.

- Flip-Chip RDL routing optimisation.

- Comprehensive support for physical, electrical, DFM and DFT design rules.

- Pre-routing parasitics estimation, enabling early system static timing analysis.

Genio Product Family Options

The Genio product family consists of 2D, 2.5D and 3D options, which enable different sets of features particular for the style of system packaging. All three options are included in the bundle available through Europractice.

2D

Genio 2D allows simple two dimensional IC system architectures to be integrated in a package, enabling IO planning and optimisation. A wide variety of package configurations and assembly methods are supported, including wire bonding and flip-chip.

2.5D

Genio 2.5D is aimed at systems with more vertical integration through the use of interposers, and enables analysis and optimisation of interconnect system interconnect and through Silicon Vias (TSV).

3D

Genio 3D enables optimisation of IO and interconnect for a stack of ICs in a package, supporting traditional 3D package assembly, along with advanced 3D methods such as pure flip-chip using TSV for vertical interconnect. Included is stack planning optimisation, which identifies the optimal stack order for ICs.

| Feature | 2D | 2.5D | 3D |

|---|---|---|---|

| Stack planning optimisation | NA | NA | INC |

| TSV management and optimisation | NA | INC | INC |

| RDL feasibility router | OPT | OPT | OPT |

| I/O ruing builder | OPT | OPT | OPT |

| Multi Level (>2) | NA | INC | INC |

| Multi chip per level | OPT | INC | NA |